# Design and Analysis of Wideband Low Noise Amplifier for Multiple Wireless Applications

<sup>1</sup>Ankita A. Pawade, <sup>2</sup>Bhushan R. Vidhale, <sup>3</sup>Dr. M.M. Khanapurkar

<sup>1</sup>Research Scholar, Department of Electronics & Telecommunication Engineering,

<sup>2</sup>Research Scholar, Department of Electronics & Telecommunication Engineering,

<sup>3</sup>Professor and Head, Department of Electronics & Telecommunication Engineering,

G. H. Raisoni College of Engineering, Nagpur, Maharashtra – 440016 India.

E-mail- pawadeankita3@gmail.com

Contact No- +91-9096362065

**Abstract**— Effective communication requires an ideal lossless transmitter–receiver. Low Noise Amplifier being the front end of any receiver requires to be highly efficient. With the development in technology the need of multiband receiver capable of supporting multiple standard applications has emerged. This requires integrating of various band of frequency for a single device. Therefore researchers are working over developing wideband receiver with wideband Low Noise Amplifier (LNA). LNA being the chief component of radio receiver has to have highest gain with low noise figure so that the signal retrieved at later stages are lossless. LNA design is a crucial task as it requires proper management of trade-off between all it's parameters including gain, noise figure, stability, and power consumption .The CMOS LNA is designed and simulated using Advanced Design System (ADS).

Keywords- Matching, Stability, Noise figure, Gain, Trade-off, Radio receiver, Reflection Coefficient

## INTRODUCTION

With the advancements in the world, technology is advancing simultaneously. Along with technology communication and especially wireless communication has observed tremendous positive changes. Over past decade wireless communication has evidenced introduction of various communication standards.But each communication standard and its respective applications and advantages is limited to the frequency band it operates at. To overcome this limitation there is a need of analog circuits which would convert radio signals to required lower frequencies, appropriate for digital processing. It's the radio receiver's front end that performs this chief function. Each communication standard has it's limitation in terms of it's band of frequency and thereby it's respective applications. But with fastly advancing technology, demand for compact devices that would support multiple applications has also been observed. For fulfilling this demand, requires multiple transreceiver but this would increase the cost and complexity of device and would also require large chip size. Therefore the researchers has now targeting to developa mobile terminal that individually support multiple communication standards and it's applications.

Low noise amplifier (LNA) that is basically the first section of any radio receiver, determines the overall efficiency of receiver. The LNA determines the performance of device in terms of it's linearity, sensitivity and power consumption. LNA practically is a electronic amplifier that amplifies the weak signals and reduce noise and other distortions present in the signal it process. The main requirement of LNA is high gain and low noise figure. The LNA design requires consideration of it's prime parameters that include; gain, power consumption, noise figure, stability and linearity. But Low noise amplifier (LNA) designing includes managing proper trade-off between it's mentioned parameters as further the noise figure of LNA solely determines the overall noise figure of the system.

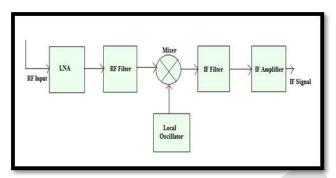

Fig 1. RF Receiver with Low Noise Amplifier

## WIDEBAND CONCEPT

Low noise amplifier (LNA) is the prime component of radio receiver circuit as it plays a vital role in defining the efficiency of receiver. Wideband Low noise amplifier (LNA) is basically the one with closed-to or exactly same operating characteristics over wide passband. Wideband LNA with highest possible gain and minimum noise figure, increases the efficiency of radio receiver and reduces the noise figure of subsequent receiver stages over a complete wide range of frequency. Therefore while designing LNA for wide range of frequency it isnecessary to boost the gain thereby keeping the noise effect as low as possible so that the signal can be retrieved effectively at the later stages.

## LNA DESIGN PROCEDURE

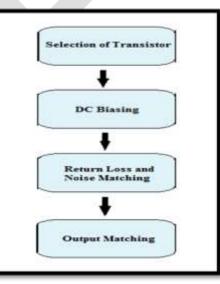

LNA design being a crucial process requires a proper flow of process to be followed. Once the design technology is decided, the next part is to select a proper transistor. As transistor forms the core of LNA circuit, it is therefore necessary to select appropriate transistor with ideal characteristics. DC bias then is the  $1^{st}$  stage of LNA design. The DC bias should be selected such that it gives stable thermal performance, as the device should be unconditionally stable for complete range of frequency. The next step is input return loss and noise matching. Where Input return loss determines the measures of how well the system is matched well to  $50\Omega$  impedance. Last step in LNA design is output matching of the transistor. For matching and current stabilization anadditional resistor is connected in either parallel or series. In the entire design process, matching plays an important role to maximize gain of the device. Even though Noise Figure, Gain, Stability, input and output match and Linearity are all important, but all these parameters are interdependent due to which it does not always work in favour of each other. This requires carefully managing trade-off between all these equally important parameters.

Fig 2. Design Procedure of LNA

www.ijergs.org

# LOW NOISE AMPLIFIER CIRCUIT

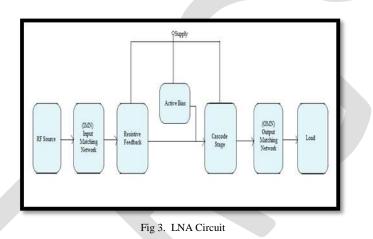

Low Noise Amplifier (LNA) is a prime component of every radio receiver circuitry. As the received signal is 1<sup>st</sup> processed through the low noise amplifier and then fed to the further stages. The performance efficiency of LNA has a huge part in defining the overall efficiency of system receiver. The LNA therefore is expected to process the signal with high gain while keeping the effect of noise and other distortions as least as possible. The design of LNA is a crucial task as it requires managing trade-off between it's parameters like gain, stability, noise figure, power consumption, while all these parameters are interdependent over each other. With the voltage supply of 1.3V, the low noise amplifier schematic below is simulated over TSMC RF CMOS 0.13µm technology.

The Low Noise Amplifier is designed over 0.13µm CMOS (Complementary Metal-oxide Semiconductor) technology. The schematic shown uses lumped dc components (R, L, C) with different value at both the input and output. The signal from RF source mostly an antenna is input to the resistive feedback network. Further the active bias provides a constant bias voltage to the transistor in cascode stage for it's proper continuous operation. The circuit uses common source topology as it requires lower bandwidth of operation. The cascode stage following the resistive feedback has many advantages as compared to other topologies. The Low Noise Amplifier is designed and simulated in Agilent's Advanced Design System software as it provides an easy to use integrated environment for circuit design at RF frequency.

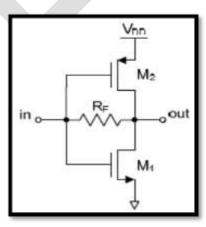

#### A. Resistive Feedback

The resistive feedback amplifier topology gives the advantage of design simplicity. Also it requires small die area and helps achieving low noise figure compared to the other amplifier topologies. Current reuse is implemented along with resistive feedback. This reduces the requirement of current and thereby helps reduces power consumption of the circuit.

Fig 4. Resistive Feedback Stage

### B. Active Bias

www.ijergs.org

The Active Bias network is designed to provide a constant bias voltage to the transistor in cascode stage. The Active bias has beneficial advantage over a dc bias. Unlike dc bias active bias is least affected by environmental and processing changes therefore assures and provides a constant bias voltage to transistor despite of the change is environment it is being operated at.

### C. Cascode Stage

Cascode amplifier stage is formed by the combination two vertically stacked transistor pair. The transistors may use any of the common-source or common-gate topology. Cascode stage provides high gain and also helps achieving better stability. It also has an advantage of good input-output isolation that helps reducing losses.

### D. Matching Network

Matching (Impedance matching) is essential part of any RF circuit design. Matching is required to transfer maximum power from source to load without any loss in power. For maximum power transfer each device in system should be well matched to it's load. A simple matching network can also be implemented using two element LC network. But depending on the type of application there are various ways of implementing matching network.

## SIMULATION RESULT

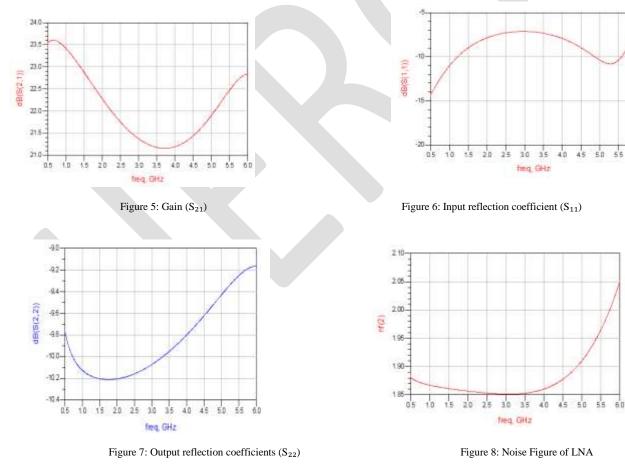

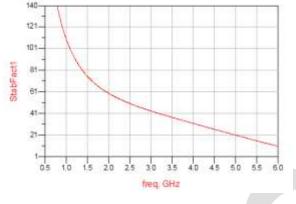

The circuit is simulated in Advanced Design System(ADS). For microwave, RF, and high-speed digital applications, Advanced Design System is a popular electronic design automation software with a powerful and easy to use interface. With 1.3V of voltage supply, S-Parameters (Scattering parameter), noise figure, harmonics and stability of the circuit for frequency range of 0.5GHz to 6GHz have been simulated.

Figure 9: Stability

The circuit is stable over the complete range of frequency. S21 (forward gain) is in the range of 23.6-22.8 db over the frequency range of 0.5-6 GHz. S11(input reflection coefficient) is in the range of -14.6 - -6.8 db, S22 (output reflection coefficient) is in the range of -9.8 - -9.2 and the noise figure is in the range of 1.89 - 2.05 db over the same frequency range of 0.5-6 GHz.

| Paper        | Frequency | Gain          | Noise          | <b>S</b> 11 | <b>S</b> 22 |

|--------------|-----------|---------------|----------------|-------------|-------------|

|              | (GHz)     | (dB)          | Figure<br>(dB) | (dB)        | (dB)        |

|              |           |               |                |             |             |

| Ref 10       | 3.1-10.6  | 12.25         | <3.8           | <-10        | <-8.2       |

|              |           |               |                |             |             |

| Ref 11       | 0.8-2.5   | 15.1          | 1.63           | <-10        | <-5.0       |

|              |           |               |                |             |             |

| Ref 12       | 1         | 19.5          | 3.81           | <-5.0       | NA          |

|              |           |               |                |             |             |

| This<br>Work | 0.5-6     | 23.6-<br>22.8 | 1.89 -<br>2.05 | -14.6       | -9.8        |

|              |           | 22.8          | 2.03           | 6.8         | 9.2         |

|              |           |               |                |             |             |

|                 | TABLE 1           |

|-----------------|-------------------|

| COMPARISON OF S | IMULATION RESULTS |

## CONCLUSION

The paper presents detail procedure and design of a wideband Low Noise Amplifier (LNA). The Low Noise Amplifier Circuit is designed in 0.13µm CMOS Technology. The designed circuit is simulated in Agilent ADS software. The simulation results of the circuit has low noise figure with considerably high gain over the entire wideband of frequency. Also designed wideband LNA is stable for entire range. The designed Low Noise Amplifier is suitable for a wideband radio receiver circuit.

#### **REFERENCES:**

- [1] Pooyan Sakian, Erwin Janssen, Arthur H. M. van Roermund, and Reza Mahmoud, "Analysis and Design of a 60 GHz Wideband Voltage-Voltage Transformer Feedback LNA," IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL.60, NO.3, MARCH 2012

- [2] Kuan-Hsiu Chien, and Hwann-Kaeo Chiou, "A 0.6-6.2 GHz Wideband LNA Using Resistive Feedback and Gate Inductive Peaking Techniques for Multiple Standards Application," Asia-Pacific Microwave Conference Proceedings, pp. 688-690, 2013

- [3] Hira Shumail, Maliha Nisar, Tooba Muzaffar, Sana Arshad and Qamar-ul-Wahab, "Fully Integrated, Highly Linear, Wideband LNA in 0.13µm CMOS Technology," IEEE Symposium on Wireless Technology and Applications, September 2013

- [4] Chang-Tsung F, Chien-Nan Kuo, Stewart S. Taylor, "Low-Noise Amplifier Design With Dual Reactive Feedback for Broadband Simultaneous Noise and Impedance Matching," IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL.58, NO.4, APRIL 2010

- [5] Gao Zhiqiang, Liu Dawei, He Shiqing, Han Haisheng, "The Design of Dual-band CMOS Low Noise Amplifier For Wireless Applications," IEEE Cross Strait Quad Regional Radio Science and Wireless Technology Conference, pp. 675-678, July 2011

- [6] Pieńkowski D., "CMOS Low-Noise Amplifier Design for Reconfigurable Mobile Terminals", Ph.D. dissertation, Von der Fakultät IV Elektrotechnik und Informatik der Technishen Universität, Berlin, 2004

- [7] Dao V.K., Bui Q.D., and Park C.S, "A Multi-band 900MHz/1.8GHz/5.2GHz LNA for Reconfigurable Radio," IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Honolulu, June 2007

- [8] Jigisha Sureja, Shruti Oza, Jitendra Thathagar, "A 0.1-3 GHz Low Power Cascode CS LNA using 0.18µm CMOS Technology", 2012 1st International Conference on Emerging Technology Trends in Electronics, Communication and Networking

- [9] Vu Kien Dao, Byoung Gun Choi, Chul Soon Park, "Dual-band LNA for 2.4/5.2GHz applications," Asia-Pacific Microwave Conference (APMC), pp. 413-416, 12-15 Dec. 2006

- [10] K. Yousef, H. Jia, R. Pokharel, A. Allam, M. Ragab and H. Kanaya, "A 0.18 µm CMOS Current Reuse Ultra-Wideband Low Noise Amplifier (UWB-LNA) with Minimized Group Delay Variations," Proceedings of the 9th European Microwave Integrated Circuits Conference 2014

- [11] Mayank B. Thacker, Manoj Awakhare, Rajesh H. Khobragade, Pravin A. Dwaramwar, "Multi-Standard Highly Linear CMOS LNA," 2014 International Conference on Electronic Systems, Signal Processing and Computing Technologies

- [12] Arunkumar Salimath, Pradeep Karamcheti, Achintya Halder, "A 1 V, sub-mW CMOS LNA for Low-power 1 GHz Wideband Wireless Applications," 2014 27th International Conference on VLSI Design and 2014 13th International Conference on Embedded Systems

- [13] Lei Liao, Stefan Kaehlert, Yifan Wang, Aytac Atac, Ye Zhang, Martin Schleyer, Ralf Wunderlich, and Stefan Heinen, "A Low Power LNA for Bluetooth Low Energy Application with Consideration of Process and Mismatch," Proceedings of APMC 2012, Kaohsiung, Taiwan, Dec. 4-7, 2012

- [14] Abdelkader Taibi, Abdelhalim Slimane, Sid Ahmed Tedjini, Mohand Tahar Belaroussi, Djabar Maafri, "A 0.9 V Low Power Reconfigurable CMOS Folded Cascode LNA For Multi-Standard Wireless Applications," 9th International Design and Test Symposium 2014

- [15] Aaron V. Do, Chirn Chye Boon, Manh Anh Do, Kiat Seng Yeo, Alper Cabuk, "A Subthreshold Low-Noise Amplifier Optimized for Ultra-Low-Power Applications in the ISM Band," IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, VOL.56, NO.2, FEBRUARY 200