# Design and Analysis of Low Noise Amplifier for 2.47GHz, build for Wireless LAN and WI-FI (802.11G Protocol)

Author – 1) Mr. Mayur K. Mohod (M.E. EXTC)

mayurmohod29@gmail.com

#### Mb No-9503764268

**Abstract**- The LNA function, play an important role in the receiver designs. Its main function is to amplify extremely low signals without adding noise, thus preserving the required Signal-to-Noise Ratio (SNR) of the system at extremely low power levels.

Amplification is one of the most basic and prevalent RF circuit functions in modern RF and microwave systems. Microwave transistor amplifiers are rugged, low cost, and reliable and can easily be integrated in both hybrid and monolithic integrated circuitry. To amplify the received signal in a RF system, a low noise amplifier (LNA) is required. The goal of this is to design an LNA with lowest noise figure possible, with gain as high as possible for the given FET and information. An amplifier is designed for the purpose on increasing level of voltage, current or power. The amount of this increase is known as gain on amplifier.

First stage of a receiver is typically a low noise amplifier (LNA), whose main function is to provide enough gain to overcome the noise of subsequent stages. Aside from providing this gain while adding as little noise as possible, an LNA should accommodate large signal without distortion and frequently must also prevent specific impedance, such as  $50\Omega$ , to the input source. CMOS amplifier will implement in 90 nm CMOS technology using ADS tool operating on wireless and Wi-fi Application. This ADS tool gives the advantages in the designing of LNA.

Keywords- LNA, SNR, RF, FET, CMOS, VLSI, BJT, ADS.

## INTRODUCTION-

The LNA is the first block in most receiver front ends. Its job is to amplify the signal while introducing a minimum amount of noise to the signal. Gain can be provided by a single transistor. Since a transistor has three terminals, one terminal should be ac grounded, one serves as the input, and one is the output. There are three possibilities, as shown in Figure 6.1. Each one of the basic amplifiers has many common uses and each is particularly suited to some tasks and not to others. The common-emitter amplifier is most often used as a driver for an LNA. The common-collector, with high input impedance and low output impedance, makes an excellent buffer between stages or before the output driver. The common-base is often used as a cascade in combination with the common-emitter to form an LNA stage with gain to high frequency, as will be shown. The loads shown in the diagrams can be made either with resistors for broadband operation, or with tuned resonators for narrow-band operation. In this chapter, LNAs with resistors will be discussed first, followed by a discussion of narrowband LNAs. Also, refinements such as

#### 2. Objective:-

The objective here is to develop **Low Noise Amplifier** with desired specifications. In the following project we have tried to explain how we designed an amplifier at 2.45 GHz for W-LAN application. To achieve LNA with improved gain with the help of CMOS Technology by using single stage n-MOS amplifier .Evaluation of noise figure, gain, input and output reflection coefficient. Design and simulation of RF circuit in Advanced Design Tools(ADS). We used "ADVANCED DESIGN SYSTEM 2009" for simulation

purpose. It is user friendly tool and easy to understand. ADS is the "Hi-Frequency &Hi-Speed" platform for IC, Package and Board Co-Design.

# 3. Literature review:-

• One of the important implementation of Design and noise optimization for a RF low noise amplifier by Ravinder Kumar, Manish Kumar, and Viranjay M. Srivastava in this, they proposed Amplifier is a non-linear characteristics device and causes two main problems one is blocking and other is inter-modulation

• Wenjian Chen, Tins Copani, Hugh J. Barnaby, SayfeKiaeiIn the context of A 0.13 um CMOS ultra-low power front-end receiver for wireless sensor networks they proposed feedback techniques to reduce the current consumption while optimizing the input matching and noise performance.

• Another important performance of the forward-biased RF LNA with deep n-well n-MOS transistor given byS.F. WAN Muhamad Hatta, N. Soin in this they proposed The common gate transformer feedback transconductance boosting is used to minimized the current consumption then gain is doubled due to the sum of n-mos and p-mos transconductances. The main function of LNA is mutually dependent on a set of design parameter values. LNA design with deep n-well into a fully integrated LNA with forward biasing exhibits better power gain & noise-figure performance.

4. Research methodology to be employed:-

# **STEP 1:- Selection of MOS Transistor**

This is the first and the most important step while designing an on chip LOW NOISE AMPLIFIER. The selection of MOS depends on its mobility, so we have selected an enhancement type of n-MOS transistor. The three important parameters in the transistor are  $V_{ds}$ ,  $V_{gs}$  and  $I_{ds}$ . Values of  $V_{ds}$  and  $V_{gs}$  are predetermined. We have to obtain the desired value of Ids which is dependent on W/L ratio of MOS transistor. Since we are using 0.09µm technology, our device length is fixed at 0.09 micrometer. The only parameter on which the Ids depends is "width" of the device.

# $\mathbf{I}_{ds} = \left[\frac{\mu n * cox}{2}\right] * \left[\frac{W}{L}\right] * (\mathbf{V}_{gs} - \mathbf{V}_t)^2$

Values of  $\mu_n$  and  $C_{ox}$  are dependent on fabrication process. Since we are using 0.09 $\mu$ m technology  $C_{ox} = 8.42$  fF. For simulation purpose we are using BSIM 3 model, hence the device width is reduced by 20% to 30% of the calculated width.

# **STEP 2:- DC Simulation**

Biasing in electronics is the method of establishing predetermined voltages or currents at various points of an electronic circuit to set an appropriate operating point. The operating point of a device, also known as bias point, quiescent point, or Q-point, is the steadystate operating condition of an active device (a transistor or vacuum tube) with no input signal applied.

The importance of DC simulation is to determine the quiescent point of the device MOS. The DC Simulation controller calculates the DC operating characteristics of a design under test (DUT). Fundamental to all RF/Analog simulations, DC analysis is used on all 549 <u>www.ijergs.org</u>

RF/Analog designs. It performs a topology check and an analysis of the DC operating point, including the circuit's power consumption. The simulator computes the response of a circuit to a particular stimulus by formulating a system of circuit equations and then solving them numerically. The DC simulation accomplishes this analysis as follows:

- Solves a system of nonlinear ordinary differential equations (ODEs)

- Solves for an equilibrium point

- All time-derivatives are constant (zero)

- System of nonlinear algebraic equations

You can also set up the DC simulation to sweep one or more parameters, enabling you to perform tasks such as verifying model parameters by comparing the simulated DC transfer characteristics (I-V curves) of the model with actual measurements. We are using a fixed biasing scheme for DC biasing. In self bias and voltage divider bias, resistors are involved, which increase the size and parasitic effect of device. So we are using self bias to optimize the devise.

# **STEP 3:- Feedback Network Design**

Feedback can be either negative or positive. In amplifier design, negative feedback is applied to effect the following properties.

- Desensitize the gain

- Reduce non-linear distortion

- Reduce the effect of noise

- Control the input and output impedance

# **STEP 4:- S Parameter Analysis**

The fact that the average analog engineer is unfamiliar with these concepts (and has probably never used a program like Genesis before), is not a good reason not to learn and use these techniques. It is quite certain that these tools are very useful even if you are designing low frequency circuits. A few of the many reasons this statement is made are:

1) The transistors you use don't know that they are supposed to work only at audio frequencies. They are perfectly happy to oscillate at many GHz if allowed.

2) Genesis (and other programs like it) contains modules that enable you to do EM modeling of things like circuit boards. This can be quite useful in making your circuit EMI hardened (a bane of many analog circuits).

3) These tools provide new insights into analog design broadening your knowledge and capabilities; insights that may help keep you ahead of your competitors. So while understanding s-parameters and having access to tools like Genesis is critical for the RF and high frequency, wide bandwidth analog designer, they are extremely useful for the low frequency analog designer as well.

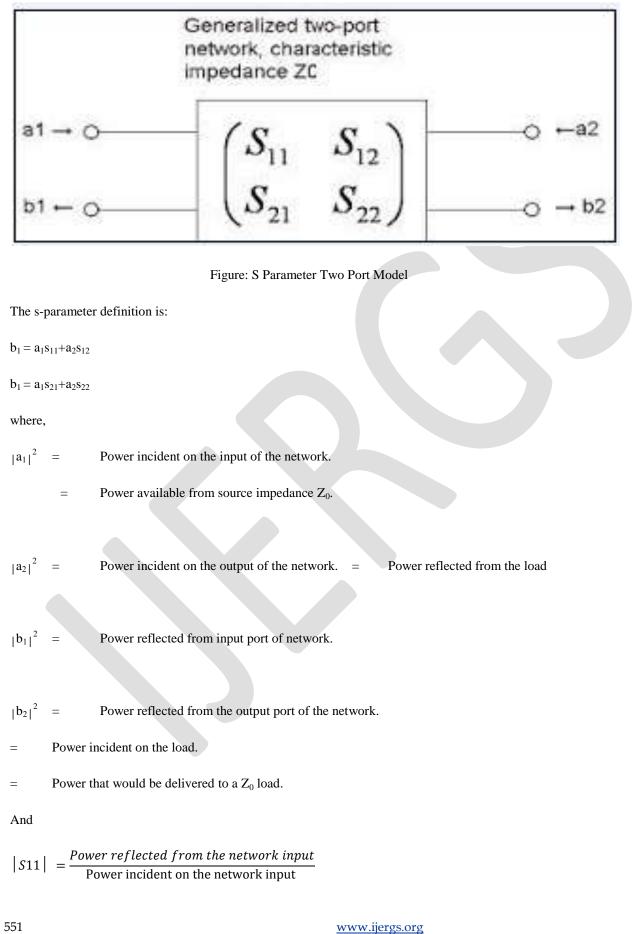

Scattering parameters are all about power; both reflected and incident in a linear two port system. It assumes that the system must be treated like a transmission line system; lumped elements no longer adequately describe the system. For the following analysis, refer to Figure 6.10.

$$|S22| = \frac{Power reflected from the network output}{Power incident on the network output}$$

$|S21| = \frac{Power \ delivered \ to \ a \ Zo \ load}{Power \ available \ from \ Zo \ source}$

= Transducer power gain with both load and source having impedance as Zo.

|S12| = Reverse Transducer power gain with Zo load and source

#### **STEP 5:-** Noise Figure Analysis

Besides stability and gain, another important design consideration for a microwave amplifier is its noise figure. In receiver applications, it is often required to have a preamplifier with as low a noise figure as possible, as the first stage of a receiver front end has the dominant effect on the noise performance of the overall system. The noise figure parameter, N, are given where, the quantities  $F_{min}$ ,  $\Gamma_{opt}$  and  $R_N$  are the characteristics of the transistor being used and are called the noise parameters of the device.

## **STEP 6:- Impedance Matching**

The impedance matching network is lossless and is placed between the input source and the device. The need for matching network arises because amplifiers, in order to deliver maximum power to a load, or to perform in a certain desired way must be properly terminated at both the input and the output ports. The impedance matching networks can be either designed mathematically or graphically with the aid of Smith Chart. Several types of matching networks are available, but the one used in this design is open single stubs whose length is found by matching done using smith chart manual.

It is necessary to match this impedance to the impedance of the source driving the circuit. The output impedance must be similarly matched. It is very common to use reactive components to achieve this impedance transformation, because they do not absorb any power or add noise. Thus, series or parallel inductance or capacitance can be added to the circuit to provide an impedance transformation. Series components will move the impedance along a constant resistance circle on the Smith chart.

## **STEP 7:-** Power Analysis

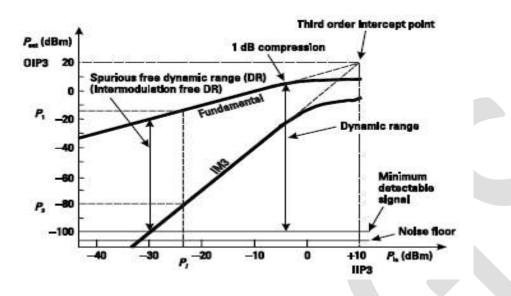

## a) Third-Order Intercept Point

One of the most common ways to test the linearity of a circuit is to apply two signals at the input, having equal amplitude and offset by some frequency, and plot fundamental output and inter-modulation output power as a function of input power as shown in Figure 5.7. From the plot, the *third-order intercept point* (IP3) is determined. The third-order intercept point is a theoretical point where the amplitudes of the intermodulation tones at  $2V_1 - V_2$  and  $2V_2 - V_1$  are equal to the amplitudes of the fundamental tones at  $V_1$  and  $V_2$ . From table 5.1, if  $V_1 = V_2 = V_i$ , then the fundamental is given by

$F_{und} = k_1 V_i ((9/4) k_3 v_i^3)$

The linear component of the above equation can be given by 552

www.ijergs.org

$$\mathbf{F}_{\text{und}} = k_1 V_i$$

can be compared to the third-order inter modulation term given by

Figure 5.7: Plot of input output power of fundamental and IM3 versus input power.

# 5. Expected Outcome and Future Work:-

In this project the Low Noise Amplifier will be design in ADS and will meet the following specification

- 1. Frequency : 2.47GHz

- 2. Gain : 14.0dB

- 3. Noise Figure : 0.5dB

- 4. IRL and ORL less than -12 db

- 5. DC Current=1 mA

# 6. ACKNOWLEDGMENTS

We take this opportunity to express our deep sense of gratitude and while hearted thanks to my project guide **Prof.V.B.Padole** for his invaluable guidance, inspiration and encouragement. It is because of them that we could synchronize our efforts.

We also express our sincere thanks to our Department for her tremendous support, encouragement and invaluable guidance throughout completion of my work.

We shall be failing in our duties until and unless we express our sincere thanks to all the members and our friends who have directly or indirectly contributed of my work.

# 7. CONCLUSION

In this way I have design Low noise amplifier for IEEE 802.11 protocol by using Advance digital design system. ADS platform easy for implementation and working with, so it is most joyful and tough work to design LNA wth improved parameter as already present in the market. Also this improved LNA also helpful for society and technical aspirant to study ADS and LNA in details.

# **REFERENCES:**

[1] AminaMsolliNasri, AbdelhamidHelali, HassenMaaref, Faculty of Sciences of Monastir, Tunisia "Ultra low power Low Noise Amplifier design for 2.4GHz application".

[2] Jing Li, Runbo Ma, Liping Han, Rongcao Yang, and Wenmei Zhang college of physics and electronics shanxi university "A co-design study of Low Noise Amplifier and Band-Pass filter. 2012 IEEE.

[3] Ravinder Kumar, Munish Kumar, and Viranja"Design and noise optimization for a RF low noise amplifier,"vol 3.

[4] S.F. WAN MuhamadHatta, N. Soin, "Performance of the forward-biased RF LNA with deep n-well n-MOS

transistor," Proc. Of IEEE Int. Conf. OnSemiconductor Electronics, Malaysia, Nov.2008.

[5] Viranja M. Srivastava, K. S. Yadav, and G. Singh "Design and performance analysis of cylindrical

surrounding double-gate MOSFET for RF switch," Oct.2011

[6] CMOS Ultra-Low Power Front-End Receiver for Wireless SensorNetworks"; IEEE Radio Frequency Integrated Circuits (RFIC)Symposium, 2007.

[7] Morici, A.; Rodriguez, S.; Rusu, A.; Ismail, M.; Turchetti, C., "A3.6mW 90 nm CMOS 2.4 GHz receiver front-end design for IEEE802.15.4 WSNs", International Symposium on Signals, Circuits and Systems, 2009.

[8] Sasilatha, T.; Raja, J., "A 1V, 2.4 GHz low power CMOS receiverfront end for wireless micro sensor nodes", International ConferenceonCommunications, Signals and Coding, 2008.

[9] Chihoon Choi; Joonwoo Choi; Ilku Nam, "A low noise and highlylinear 2.4-GHz RF front-end circuit for wireless sensor networks", IEEE 9th International Conference on ASIC (ASICON), 2011.

[10] Narendra,K.; M,S,Bhat., "Design of CMOS RF Receiver Front-endfor IEEE 802.11b", International Conference on Electronic Design,2008.

## www.ijergs.org

554

[11] Datta, S.; Dutta, A.; Datta, K.; Bhattacharyya, T.K., "Pseudo Concurrent Quad-Band LNA Operating in 900 MHz/1.8 GHz

and 900MHz/2.4 GHz Bands for Multi-Standard Wireless Receiver," IEEE24th International

[12] CihanKarakuzu. "Fuzzy logic based smart traffic light simulator design and hardware implementation". Kocaeli University, Engineering Faculty, Electronics & Tell. Eng. Department, 41070 VezirogluYerleskesi, Izmit-Kocaeli, Turkey.