# FPGA Implementation of Safe Mode Detection and Sun Acquisition Logic in a Satellite

Dhanyashree T S<sup>1</sup>, Mrs. Sangeetha B G, Mrs. Gayatri Malhotra <sup>1</sup>Post-graduate Student at RNSIT Bangalore India, dhanz1ec@gmail.com, +919482153794

**Abstract**— Satellite/spacecraft enter into Safe Mode in case of contingency when the solar panel is not rotated towards Sun in order to provide full solar array power. The transition from safe mode to sun pointing mode, carried out automatically by Sun acquisition logic. In sun acquisition logic selected yaw and roll errors are used as inputs to controller whose outputs are routed to thruster selection logic. On Safe Mode enable condition, based on the safe mode pulse from on board computer (OBC) thruster block reconfiguration is done. This initiates thruster selection logic (TSL), whose outputs are routed to thruster drivers to fire the thrusters in satellites/spacecraft to change the spacecraft orientation. The eclipse condition is also detected from 4PI pitch output on safe mode.

**Keywords**—Pitch, yaw, roll, safe mode detection, loop-on pulse generation, long pulse detection, thruster selection, sun pointing mode .

## INTRODUCTION

Communications satellite or a weather forecasting satellite or even a remote sensing satellite, irrespective of the intended application, all the satellites have several things in common. They have a metal or composite frame and body, usually known as the bus, a source of power (usually solar cells) and batteries for storage, a radio system and antenna for Telemetry, tracking and command (TT&C), an attitude control system and an onboard computer system to control and monitor the different systems[1].

The purpose of On Board Computer (OBC) system is to integrate and miniaturize Spacecraft Electronics to match the global trend and meet the requirements of Autonomous spacecraft operations. Cost-effective spacecraft engineering is achieved by integrating the various elements of the spacecraft bus that realize the functions of command processing, Data acquisition and processing, Attitude and Orbit control, Telemetry and Housekeeping and Thermal Management into a single OBC. The MIL STD 1553B protocol is used for interfacing with various sub-systems of the spacecraft. The OBC interfaces with sensors (attitude and temperature), actuators, power, thermal control elements like heaters and Solar Array Drive Assembly through special interfaces, TTC (RF) for command and housekeeping TM[2][3]. For all these operations a functionally redundant OBC is present. In case of failure or contingency in main and redundant OBC, a separate package is configured, which houses 4Pi Sun Sensor based Hardware based Safe Mode detection and Sun Acquisition and Contingency Telemetry logics.

This paper describes the implementation of this package on a FPGA. The design implemented is synthesized and simulated, where simulation results show the detection of safe mode and thruster controls for sun acquisition.

# METHODOLOGY

#### A. Terminology

Safe mode is an operating mode of a modern spacecraft during which all non-essential systems such as science instruments are shut down and only essential functions such as thermal management, radio reception and attitude control are active. Safe mode is entered automatically upon the detection of sun absence. The spacecraft attempts to maintain orientation with respect to the Sun for illumination of solar panels and for thermal management. The spacecraft then awaits radio commands from its mission control center monitoring for signals on its low-gain omnidirectional antenna[4].

This system uses coordinates that maintain their orientation relative to the earth as spacecraft moves in orbit. These coordinates are known as roll, pitch, and yaw or RPY, and are illustrated in figure 1. In this system, the yaw axis is directed toward the nadir (i.e., toward the center of the Earth), the pitch axis is directed toward the negative orbit normal, and the roll axis is perpendicular to the other. Thus, in a circular orbit, the roll axis will be along the velocity vector[6].

Fig 1. Satellite's position w.r.t.to the Earth and the Sun

#### B. Implementation overview

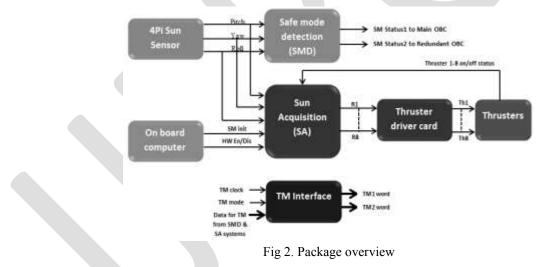

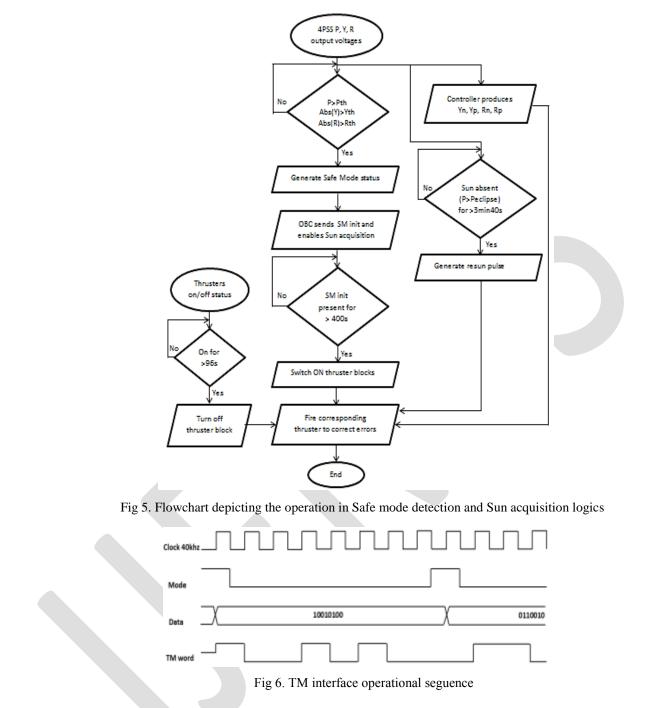

Safe mode detection, Sun acquisition and telemetry interfacing are the three basic logics designed and implemented as shown in figure 2. Safe mode detection logic produces safe mode initiation status. After which thrusters are controlled by sun acquisition logic. The status of the signals used and manipulated in these two logics is sent to telemetry(TM) subsystem after interfacing with TM interface logic.

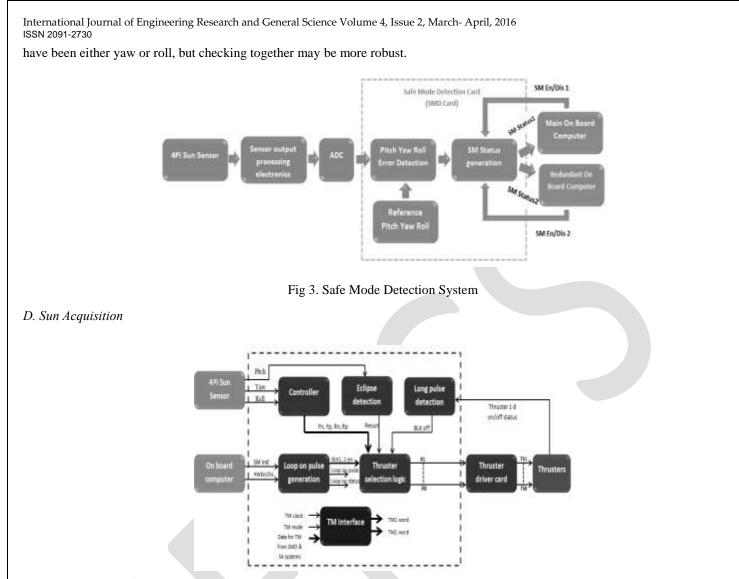

#### C. Safe mode detection

Safe mode detection logic shown in figure 3 is based on 4Pi sun sensors pitch, yaw and roll signals errors. Selected sensor outputs are compared with respect to threshold set to detect errors in sensors signals. The Sun will be on negative pitch axis, when the solar panels are normal to the Sun. The 4pi pitch output magnitude will be high when the Sun is directly looking at the pitch cells. So when the Sun is on negative pitch side, the pitch output will be -5.0 volts that is high in magnitude[5].

The presence of error is verified by the following conditions.

- 1. If 4pi pitch output greater than the threshold (for example, 1.5 volts is greater than 1.0 volts). This check is to say that the Sun is away from the body negative pitch axis.

- 2. If absolute values of 4pi yaw or roll outputs (magnitudes alone) are beyond certain threshold (say, 1.5 volts). This check is to ensure that the Sun is beyond the cone of  $45^{\circ}$  about the negative pitch axis.

The second condition supports the 4pi pitch output checking. The check also supports logic validity during eclipse. Checking could

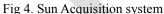

In sun acquisition logic selected pitch, yaw and roll errors are used as inputs to controller whose outputs are routed to thruster selection logic. The sun acquisition system is shown in figure 4. On Safe Mode enable condition, the SM pulse from OBC initiates a 400sec timer whose outputs do thruster block reconfiguration. Thruster selection logic (TSL) is initiated after obtaining assertions from block reconfiguration logic. The TSL outputs are routed to thruster drivers. The thruster outputs in turn change the spacecraft orientation. The sensor data will sense it and controller (closed loop) will change the thruster firing duration accordingly. The eclipse condition is detected from 4PI pitch on safe mode condition. If eclipse is detected, sun acquisition is initiated on end of eclipse. The duration of eclipse is based on mission / orbit. Long pulse detection logic makes thrusters block off, if any of the thrusters is firing for more than 96 sec. The flow diagram depicting the operation sequence of safe mode detection and sun acquisition is shown in figure 5.

## E. TM Interface

When in Safe mode, the satellites rejects on-board stored commands and relies on the ground for the transition back to normal mode. To support ground investigation and recovery actions, the observability is ensured through telemetry, which provides sensors acquisition data, status of essential signals of safe mode detection and sun acquisition logics.

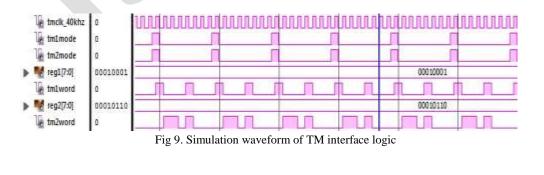

The TM word to be sent is provided by TM interface logic. The operational sequence of this logic is represented in figure 6. The clock rate at which TM interface is done is 40Khz. With the telemetry mode pulse, status of signals is latched into an 8 bit register and is serially interfaced to TM subsystem.

## F. Testing

The design is implemented on Spartan family FPGA. Xilinx ISE design suite software tool is used for synthesis on FPGA and analysis of HDL designs. For testing purpose the outputs of 4Pi sun sensor are provided using voltage sources. These analog outputs are fed to ADC to get the digitized values before inputting to FPGA. ADC used for testing purpose is of Analog device's AD7891 family ADC. Possible range of pitch, yaw and roll voltages are fed to verify the correctness of design. The signals from OBC to be used in the design are given externally by a voltage source for testing.

# SIMULATION RESULTS

The Safe mode detection and Sun acquisition logic is designed using VHDL code and is synthesized on Spartan family FPGA[7][8]. The synthesized design is simulated for different test cases. The design coded using editor in Xilinx ISE design suite is simulated

www.ijergs.org

862

using the Xilinx ISE simulator (version 12.1). The results of the simulation are shown in the waveform.

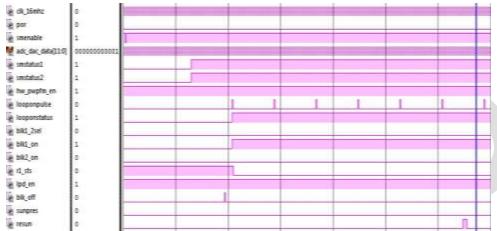

Simulation results of Safe Mode Detection logic is shown in figure 7. For given pitch, yaw and roll voltage, as the error is present, the design detects the error and safe mode is initiated by SM Status signal transition from low to high logic. This shows that SM detection logic detects the sun absence.

Simulation results also show the loop on pulse and status generated for the test values. The results show whether the thruster blocks will be turned on or off with the BLK on signals. As one of the thruster statuses is held high for more than 96s for testing purpose, the BLK off pulse is generated, as seen on simulation waveform.

Fig 7. Simulation waveform of safe mode detection logic, loop on pulse generation, long pulse detection and eclipse detection logic

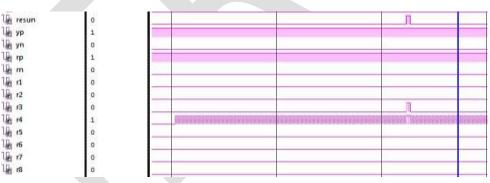

Figure 8 shows the outputs of thruster selection logic, where firing pulses are continuously given to thruster 4, based on the yp, yn, rp, rn signals. Pulse width increase and thruster 3 turning on along with thruster 4 can be seen when resun pulse is generated detecting eclipse.

Fig 8. Simulation waveform of thruster selection logic

Simulation result of TM interface logic is shown in figure 9, where the operational sequence is simulated and TM data words are serially transmitted.

www.ijergs.org

## CONCLUSION

Through this work, the architecture and function of the package consisting safe mode detection, Sun acquisition and TM interfacing, have been implemented on FPGA. Safe mode is detected based on the 4Pi sun sensor outputs, which indicates the loss of sun presence. This is followed by transition, from safe mode to sun pointing mode, carried out by sun acquisition logic which controls thrusters to orient solar arrays to point to sun. The scope of the future development is since the design is implemented using VHDL code, it is easy to add new features and design is target independent. The design can be targeted on to any family of FPGA/ASIC.

#### **REFERENCES:**

- [1] Anil K. Maini, Varsha Agrawal-"Satellite technology: Principles & applications", John Wiley & Sons Ltd., Publication

- [2] Preliminary design review document of on board computer for CARTOSAT-2C, ISRO

- [3] Comprehensive design document on spacecraft bus management unit(hardware) of CARTOSAT-2/2A/2B, ISRO

- [4] Vinod Kumar, A.K.Kulkarni, K.Parameshwaran, R. Pandiyan and N.K.Malik, "On-Board Autonomy For ISRO Geosynchronous Spacecraft", IAA-AAS-DyCoSS1-01-10

- [5] Yasir, M.; Grillmayer, G.; Roeser, H.-P. "Development of a safe mode attitude control for a FPGA based micro satellite", Multitopic Conference, 2008. INMIC 2008. IEEE International, On page(s): 42 - 46

- [6] Marcel J. Sidi, "Spacecraft dynamics and control: a practical engineering approach", Press Syndicate of the University of Cambridge publication

- [7] Andrew Rushton, "VHDL for Logic Synthesis", John Wiley & Sons, Ltd. Publication, 2011

- [8] Peter J. Ashenden, "The Designer's Guide to VHDL", Elsevier Inc publication, 2008